#### Национальный исследовательский ядерный университет «МИФИ»

На правах рукописи

#### ДОМОЖАКОВ ДЕНИС АЛЕКСАНДРОВИЧ

Dan

# СЛОЖНО-ФУНКЦИОНАЛЬНЫЕ БЛОКИ МУЛЬТИСКОРОСТНЫХ ПРИЕМОПЕРЕДАТЧИКОВ ПОСЛЕДОВАТЕЛЬНЫХ КАНАЛОВ ДЛЯ КМОП СБИС «СИСТЕМА НА КРИСТАЛЛЕ»

Специальность 05.13.05 — Элементы и устройства вычислительной техники и систем управления

Автореферат диссертации на соискание ученой степени кандидата технических наук

Автор: Доможаков Денис Александрович

Диссертация выполнена в Национальном исследовательском ядерном университете «МИФИ»

Научный Кондратенко Сергей Владимирович

**руководи-** кандидат технических наук, доцент кафедры **тель**: «Электроника» (№3) НИЯУ МИФИ, г. Москва

Официальные оппоненты:

доктор технических наук, профессор НИУ МИЭТ

Крупкина Татьяна Юрьевна

доктор технических наук,

заместитель генерального директора по научной работе АО «НПП «Салют» Оболенский Сергей Владимирович

кандидат технических наук,

старший научный сотрудник ФИЦ ИУ РАН

Дьяченко Юрий Георгиевич

Защита диссертации состоится « » мая 2022 г. в часов на заседании диссертационного совета МИФИ.05.03 в Национальном исследовательском ядерном университете «МИФИ» по адресу: 115409, г. Москва, Каширское шоссе, 31.

С диссертацией можно ознакомиться в библиотеке НИЯУ «МИФИ» и на сайте ds.mephi.ru.

Ученый секретарь диссертационного совета, к.т.н

Веселов Денис Сергеевич

#### ОБЩАЯ ХАРАКТЕРИСТИКА ДИССЕРТАЦИИ

Диссертация посвящена решению важной научно-технической задачи разработки критичных блоков и мультискоростных приемопередатчиков последовательного канала в целом, изготавливаемых по объемной КМОП технологии и предназначенных для построения отечественных СБИС типа «система на кристалле» (СнК).

#### Актуальность проблемы

Эффективная работа цифровой вычислительной системы невозможна без обеспечения надежного обмена данными между блоками в её составе. Функцию высокоскоростного обмена цифровыми данными между блоками внутри системы зачастую выполняют мультискоростные приемопередатчики последовательных каналов (МСПП), иначе называемыми SerDes приемопередатчиками. Целесообразность реализации широкого диапазона перестройки скоростей МСПП (от единиц и десятков Мбит/с до нескольких Гбит/с, а в отдельных применениях свыше 10 Гбит/с) - особенность именно отечественных разработок, которые должны закрывать, по возможности, потребности множества применений в условиях ограниченного выбора у потенциальных пользователей изделий отечественного производства. Следует отметить, что функция перестройки битовой скорости обмена в широком диапазоне, не характерная для зарубежных аналогов, существенно увеличивает трудоемкость процесса разработки.

За последние десятилетия наблюдается стремительный рост битовых скоростей передачи данных по последовательным каналам. Растет сложность и время разработки МСПП. Разработка быстродействующих приемопередатчиков со скоростями 2,5 Гбит/с и более сопряжена с решением сложных задач, нацеленных на выявление и обеспечение требуемого уровня быстродействия критичных блоков МСПП. К таким задачам относятся построение и оптимизация цепей тактовых сигналов, проектирование периферийных блоков, минимизация влияния паразитных элементов, борьба с технологическим разбросом и др. В то же время проектирование остальных блоков из состава МСПП, которые либо работают на пониженных скоростях, либо могут быть реализованы на основе библиотечных элементов (из стандартных или специализированных библиотек), не сопряжено с появлением сложных проблем и может быть выполнено с использованием штатных средств применяемой САПР.

Одним из основных показателей качества работы МСПП и, шире, всего класса приемопередатчиков является частота возникновения битовых ошибок (BER). В соответствии с требованиями к современным приемопередатчикам ответственного применения BER не должен превышать  $10^{-12}$ , в отдельных случаях —  $10^{-15}$ .

В настоящее время в достаточной мере освоены методы и средства измерения ВЕR. Выпускаются осциллографы с опцией анализа глазковых диаграмм и определения связанного с ними показателя BER, а также

специализированные измерители BER. Практически стала стандартной опция, ориентированная на применение для измерения BER встраиваемых на кристалле генераторов псевдослучайных последовательностей.

В то же время прямой анализ при моделировании, аналогичный физическим измерениям по подсчету числа ошибок, на этапе проектирования, требует существенного времени (от нескольких дней до недель в зависимости от точности результата и использования методов экстраполяции). На практике расчет показателя ВЕК в процессе проектирования чаще всего заменяется анализом параметров глазковых диаграмм исходя из расчетов на наихудший случай при объеме вычислений, который недостаточен для получения статистически значимых результатов и ограничивает возможности проектировщика по выбору и сравнению альтернативных решений в процессе параметрических расчетов. Разработка полуаналитической модели приемопередающего тракта, а также применение на её основе методики расчета ВЕК на этапе проектирования, с целью выбора архитектуры и выделения критичных блоков для их последующей оптимизации являются актуальной задачей. Время, выделенное на этот расчет, не должно превышать нескольких часов.

Таким образом, для целого ряда приложений актуальна постановка и решение задачи проектирования отечественных СФ-блоков МСПП, не уступающих по совокупности основных характеристик зарубежным аналогам, а по диапазону перестройки скоростей, превосходящих их. Создание собственной методики проектирования МСПП, позволяющей контролировать значение показателя BER в процессе проектирования, а также применение этой методики при разработке сложно-функциональных блоков и СБИС СнК, включающих МСПП и изготавливаемых по КМОП технологии, является актуальной задачей.

## Текущее состояние проблемы исследования и её предмет

Анализу механизмов возникновения битовых ошибок в приемопередающем тракте посвящено большое число публикаций на данную тему. В настоящее время разработана теория джиттера, способы его контроля и снижения влияния в процессе передачи сигнала в приемопередающем тракте как основной причины появления ошибок, которые могут возникнуть в периферийной части приемника при восстановлении потока цифровых данных. В настоящее время разработана теория джиттера как основной причины появления ошибок при передаче сигналов после нормализации их по амплитуде, выполняемой в периферийной части приемника. Известны методики исследования джиттера передаваемого сигнала данных и разложения его на компоненты для последующего анализа работы приемопередающего тракта. Множество работ посвящено беспроводным интерфейсам и влиянию линии передачи на качество связи. Хотя областью применения рассматриваемых в данной работе МСПП являются высокоскоростные проводные соединения (прежде всего, согласованные трассы на печатных

платах и витые пары), предлагаемые автором методики и специализированные средства проектирования таких МСПП, очевидно, могут быть востребованы как для беспроводных, так и для перспективных оптоэлектронных соединений в части реализации внутрикристальной обработки и передачи электрических сигналов.

Анализ информации по теме диссертации показал, что большое внимание уделяется измерению BER разработанных образцов приемопередатчиков, в том числе развитию встроенных систем самотестирования приемопередатчиков, повышению точности и информативности физических измерений, анализу и разработке систем восстановления тактового сигнала из принимаемого потока данных, а также методам и средствам восстановления формы (целостности) сигнала с использованием предыскажений в передатчиках и эквалайзеров в приемниках. Вместе с тем, в известных работах не уделяется достаточного внимания анализу и реализации альтернативных подходов количественной оценки качества разработанных и изготовленных приемопередатчиков в процессе экспериментальных исследований, альтернативных по отношению к прямому измерению показателя BER. Автор, наряду с прямыми измерениями показателя BER использовал для этого, в частности, анализ состояния статусных цифровых сигналов в приемнике. Такой подход отличается высокой чувствительностью к проблемным ситуациям и сохраняет удобство анализа цифровых сигналов.

В известных работах представлено множество частных вариантов построения этих критичных блоков, а также методик и специализированных средств проектирования высокоскоростных приемопередатчиков, которые, однако, не предоставляют разработчику возможность полного и оперативного контроля за достижимой величиной BER в процессе проектирования и не учитывают особенности мультискоростных приемопередатчиков.

Анализ текущей ситуации с анализом показателя BER, как основного интегрального показателя качества работы МСПП, выявил следующие особенности:

- Известны методики оценки BER, нацеленные на сокращение затрачиваемого на расчеты времени, однако они не всегда адаптированы для интеграции с используемыми в процессе проектирования электронных устройств САПР либо недоступны сторонним пользователям.

- Существуют специализированные пакеты расчета BER приемопередающих трактов (MATLAB пакет Bit Error Analysis Tool). Однако область применения данного пакета ограничена расчетом беспроводных МСПП и имеет узкий набор входных параметров.

- В целом можно констатировать значительное внимание к расчету показателя BER трактов передачи данных. Однако, в доступных автору публикациях уделяется недостаточное внимание анализу

внутреннего устройства блоков в составе МСПП в части их влияния на показатель BER. Основное внимание уделяется методам и средствам измерения джиттера и показателя BER изготовленных образцов приемопередатчиков.

**Целью** диссертации является повышение надежности передачи информации по последовательным каналам периферийными мультискоростными приемопередатчиками за счет снижения относительного числа битовых ошибок путем применения при проектировании приемопередатчиков предложенной полуаналитической модели тракта передачи.

Для достижения данной цели необходимо решение следующих задач.

- 1. Разработка обобщенной полуаналитической модели тракта передачи данных, предназначенной для расчета BER в процессе проектирования МСПП.

- 2. Обоснование выбора различных интерфейсов на физическом (интерфейсном) уровне реализации приемопередатчиков исходя из совокупности требований к проектируемым приемопередатчикам в целом (скорость или диапазон скоростей передачи, соответствие заданному стандарту, потребляемая мощность и др.).

- 3. Разработка универсальной методики проектирования высокоскоростных приемопередатчиков последовательных каналов, основанной на анализе зависимости величины BER от характеристик блоков, входящих в тракт передачи цифровых данных.

- 4. Апробация и использование разработанной методики при проектировании МСПП.

- 5. Экспериментальное исследование изготовленных блоков МСПП.

# Научная новизна диссертации

- 1. Разработана новая полуаналитическая модель тракта передачи, которая предусматривает анализ передаваемых кодовых последовательностей на основе выборок с присвоением весовых коэффициентов.

- 2. Впервые, помимо показателя BER, обосновано использование частоты битовых ошибок при передаче логического перепада как интегрального показателя качества работы приемопередатчиков последовательного канала, не зависящего от кодовой последовательности.

- 3. Реализована возможность оценки показателя BER приемопередатчиков последовательного канала на этапе проектирования, основанная на разработанной полуаналитической модели тракта передачи.

- 4. Предложена методика проектирования приемопередатчиков последовательного канала, основанная на анализе и минимизации показателя BER, зависящего от параметров, определяющих качество работы критичных элементов тракта при их реализации как заказных блоков.

- 5. Обоснован и реализован метод стабилизации коэффициента передачи фазы контура ФАПЧ в диапазоне температур и с учетом разбросов

технологического процесса, основанный на параметрической стабилизации блоков в составе контура ФАПЧ.

# Практическая значимость результатов диссертации

- 1. Методика расчета показателя BER на этапе проектирования использована при разработке критичных заказных блоков мультискоростных приемопередатчиков последовательного канала, работающих на скоростях от 5 Мбит/с до 12,5 Гбит/с по КМОП технологиям объемного кремния уровня от 180 нм до 40 нм.

- 2. Методика проектирования приемопередатчиков последовательного канала, основанная на анализе и минимизации показателя BER, использована при разработке оптимальной архитектуры конвейера данных передатчика и приемника, а также при обосновании эффективности метода форматирования битовой скорости передачи.

- 3. Выполнено объективное сравнение различных вариантов реализации устройств физического уровня на основе эскизного проектирования этих устройств с интерфейсами LVDS, VML, HSTL и CML по КМОПтехнологии и даны рекомендации по их использованию.

- 4. Предложен подход к высокоуровневому моделированию приемопередающих трактов с использованием поведенческих (табличных) моделей выбранных частей этих трактов. Подход сочетает преимущество результатов расчетов с помощью САПР сквозного проектирования по точности со сниженным временем расчетов при высокоуровневом моделировании. Написана и отлажена в среде пакета SciLab специализированная программа анализа приемопередающих трактов с использованием поведенческих (табличных) моделей.

- 5. Разработаны и реализованы блоки ФАПЧ с улучшенными точностными характеристиками: зарядно-разрядный блок с компенсацией дрейфа крутизны вольт-частотной характеристики генератора, управляемого напряжением (ГУН), ГУН со стабилизированной крутизной вольт-частотной характеристики, фильтр ФАПЧ с настраиваемыми параметрами в зависимости от битовой данных. Использование этих блоков в составе спроектированных высокоскоростных приемопередатчиков позволило обеспечить требуемую совокупность параметров элементов ФАПЧ в диапазоне рабочих температур, технологического разброса элементов схем, а также битовых скоростей.

- ментов ФАТГЧ в диапазоне расочих температур, технологического разброса элементов схем, а также битовых скоростей.

6. Разработаны набор технологически независимых синтезируемых Verilog блоков цифровой части передатчика и приемника, а также архитектура конвейера данных, включающая в себя принципы программирования битовой скорости, фазового сдвига потока данных и выбора оптимальной разрядности шины тактовых сигналов битовых операций.

# Результаты диссертации, выносимые на защиту

1. Полуаналитическая модель тракта передатчик-приемник, учитывающая зависимость показателя BER от архитектуры и от параметров,

- определяющих качество работы критичных блоков приемопередатчиков последовательного канала.

- 2. Методика проектирования приемопередатчиков последовательного канала, основанная на анализе и минимизации показателя BER при реализации критичных элементов тракта как заказных блоков.

- 3. Схемотехническая реализация блоков в составе МСПП, предназначенных для минимизации джиттера битового потока данных, включая зарядно-разрядный блок с компенсацией дрейфа крутизны ВЧХ управляемого напряжением генератора (ГУН) со стабилизированной крутизной вольт-частотной характеристики и фильтр ФАПЧ с настраиваемыми параметрами в зависимости от битовой скорости данных.

- 4. Универсальная архитектура цифровой части МСПП, примененная при разработке отечественных МСПП с низким показателем BER.

- 5. Результаты практического применения разработанной методики проектирования, эффективность которой подтверждена при создании высокоскоростных СФ-блоков МСПП с требуемыми количественными и качественными характеристиками.

#### Апробация диссертации

Основные положения диссертации докладывались и обсуждались на следующих научно-технических конференциях и семинарах:

- Всероссийская научно-техническая конференция "Проблемы разработки перспективных микро- и наноэлектронных систем": 2014 г. и 2016 (г. Зеленоград).

- Научная сессия НИЯУ МИФИ, 2015 г.

- Международный Форум «Микроэлектроника 2018», два доклада (г. Алушта).

Результаты диссертации были использованы при проведении ОКР "Схема-И8-1", "Обработка-И1", "Интерфейс-3" и "Базис-Б5" в АО НПЦ «ЭЛВИС» по разработке интерфейсных радиационно-стойких "Hard" СФ-блоков высокоскоростного последовательного канала "GigaSpaceWire/SpaceFibre", что подтверждено актом о внедрении.

# Публикации

Основные результаты диссертации опубликованы в 15-ти работах (из них 3 без соавторов) в период с 2013 по 2021 гг., в том числе 11 работ в издании из перечня ВАК России, 3 работы в изданиях, входящих в базу данных цитирования Scopus и 4 работы, входящие в базу данных цитирования Web of Science, в том числе одна работа без соавторов. Также автор является соавтором двух патентов на полезную модель и одного патента на изобретение.

# Объем и структура диссертации

Диссертация состоит из введения, четырех глав, заключения, списка литературы и приложения. Диссертация содержит 155 страниц, включая

список литературы, 71 рисунок, 21 таблицу. Список литературы включает 101 наименование.

#### Содержание диссертации

**Во введении** обоснована актуальность темы, определена цель диссертации. Приведена постановка задачи и сформулированы основные положения, выносимые на защиту. Изложена научная новизна и практическая ценность диссертации.

# ГЛАВА 1. Достигнутые характеристики, методы и средства проектирования мультискоростных приемопередатчиков последовательных каналов (МСПП)

Основные характеристики интегральных МСПП

На основании проведенного анализа характеристик МСПП выделены их основные первичные характеристики, среди которых особое внимание уделяется битовой скорости передачи Fbit и ее диапазону перестройки, а также вероятности возникновения битовых ошибок BER. Выделены также вторичные характеристики и параметры - глазковая диаграмма и джиттер, которые интегрально характеризуют качество (целостность) передаваемых сигналов в различных частях приемопередающего тракта.

Использование перечисленных и подобных им интегральных характеристик облегчает решение задачи нахождения компромиссов в процессе проектирования МСПП, так как позволяет оценить работу схем в его составе с применением небольшого числа показателей. Так, показатель ВЕК позволяет контролировать качество работы МСПП на всех этапах проектирования и производства. В данной работе автор предлагает методику разработки МСПП, решающую задачу оптимизации параметров блоков приемопередающего тракта с целью достижения требуемых значений интегральных характеристик МСПП.

Устройство МСПП и определение критичных блоков

Критичными блоками в составе МСПП являются такие блоки, которые транслируют и обрабатывают цифровые сигналы на максимальных скоростях и/или работают с не нормированными по амплитуде аналоговыми сигналами высокой частоты, что может привести к нарушению целостности этих сигналов и вызвать появление ошибок.

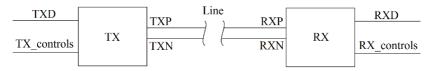

Неотъемлемые составляющие тракта передачи МСПП - передатчик, среда передачи и приемник (рисунок 1). Наборы сигналов TX\_controls и RX\_controls – сигналы настройки режимов и флаги состояний блоков.

Рис. 1. Общая структурная схема тракта передачи МСПП

Передатчик состоит из внутренней и периферийной частей:

- *Внутренняя часть* осуществляет сериализацию параллельного потока данных, поступающих на его вход, в выходной последовательный поток.

- Периферийная часть выполняет формирование выходного сигнала, пригодного для трансляции через среду передачи: усиление мощности, преобразование электрических и временных параметров, соответствующих применяемому стандарту цифрового обмена.

Приемник также включает внутреннюю и периферийную части.

- Внутренняя часть выполняет десериализацию последовательного потока данных, поступающего на его вход, в выходной параллельный поток.

- Периферийная часть производит усиление полезного сигнала, соответствующего стандартизированным электрическим и временным характеристикам и преобразование его электрических уровней в цифровой КМОП формат либо в CML (Current Mode Logic) формат.

В доступных автору информационных источниках описание архитектуры приемопередающего тракта либо отсутствует, либо представлено недостаточно детально, чтобы его можно было рассматривать в качестве прототипа. Также отсутствует описание деталей реализации критичных блоков МСПП, особенно выполненных по глубоко субмикронным технологиям. Вследствие этого задача проектирования и реализации как отдельных элементов критичных блоков МСПП, так и архитектуры приемопередающего тракта в целом является актуальной.

Критичные блоки внутренней части МСПП.

Выделены критичные блоки МСПП: периферийные части передатчика и приемника (драйвер и входной каскад с компаратором на входе), а также выходной мультиплексор передатчика и устройство фазовой автоподстройки частоты в приемнике (ВТСД), работающие в том числе с не нормализованными по амплитуде (аналоговыми) сигналами, для которых сведение всех проблем только к джиттеру не справедливо, и требуется анализ и увеличение до требуемого уровня степени раскрытия глазковых диаграмм по амплитуде.

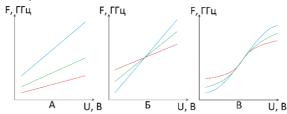

Нарушение синхронизации между блоками МСПП является прямой причиной появления ошибок передачи. Стабильность работы дерева тактовых сигналов зависит от джиттера. Одним из основных источников джиттера является система ФАПЧ. Собственный джиттер ФАПЧ напрямую зависит от параметров аналоговых блоков в его составе. Так, основной вклад в фазовый шум вносит генератор, управляемый напряжением (ГУН). Характеристики ГУН подвержены разбросу. Технологический разброс является причиной нестабильности параметров  $I_{cell}$  и  $C_{tot}$ , генерируемой частоты и крутизны ВЧХ при заданном значении управляющего напряжения. Рисунок 2 иллюстрирует три варианта ВЧХ: A- ВЧХ без стабилизации, B- со

стабилизацией определенной генерируемой частоты, B- со стабилизацией крутизны для определенной частоты.

Рис. 2. ВЧХ ГУН для типовой, наихудшей и наилучшей нормы техпроцесса: A — без стабилизации, B — стабилизация частоты, B — стабилизация крутизны

Задача стабилизации разброса частоты генерации при заданном значении управляющего напряжения является актуальной. Однако в таком случае сохраняется разброс крутизны ВЧХ, что может привести к увеличению фазового дрожания генерируемого сигнала.

Работы над минимизацией величины джиттера ФАПЧ и ВТСД привели к появлению множества архитектур и видов реализации таких блоков. Можно отметить решения, основанные на петле с задержкой (DLL), ВТСД с фазовым интерполятором, ВТСД с инжекцией заряда, ВТСД с пересемплированием и др. Каждая архитектура имеет как положительные, так и отрицательные качества.

Цифровая часть передатчика и приемника является функционально сложной. При их проектировании применимы методы автоматизированного синтеза. При этом необходимо соблюдение компромисса между быстродействием и потреблением энергии. В настоящее время заметна тенденция перевода блоков ФАПЧ и ВТСД в цифровую часть. Технологический разброс параметров компонентов интегральных схем, разброс питающего напряжения и рабочей температуры приводят к возникновению разброса величин задержек стандартных цифровых элементов.

Выходной мультиплексор – наиболее критичный блок цифровой части передатчика. Он предназначен для совершения последнего этапа сериализации: свертки двух или большего количества параллельных потоков данных в один последовательный. Увеличение размерности шины данных зачастую ведет к усложнению схемы мультиплексора, росту влияния его паразитных структур. Выбор разрядности мультиплицируемой шины данных сводится к компромиссу между удовлетворением требованию по быстродействию конвейера данных и сложностью контроля фазовых соотношений между входными потоками данных и адресными сигналами.

В известных автору работах анализ вопроса выбора размерности последней ступени сериализации передатчика представлен слабо или отсутствует. В данной работе автор проводит исследование и предлагает решение данной проблемы.

Критичные блоки периферийной части МСПП.

Произведен сравнительный анализ распространенных интерфейсов передачи данных на физическом уровне.

Периферийные блоки выпускаемых в настоящее время КМОП приемопередатчиков оперируют дифференциальными сигналами и имеют преимущественно интерфейсы CML, VML, HSTL, LVPECL и LVDS. Правильность выбора решений периферийных блоков зависит от корректности и полноты учитываемых при разработке факторов.

Драйверы на выходах периферийных частей передатчиков должны обеспечить целостность сигналов. Драйверы с выходными каскадами распространенных видов могут быть сравнены по наиболее важным критериям (скорость передачи, потребляемая мощность, качество согласования на выходе и др.). Результаты сравнения помещены в таблицу 1.

Таблица 1. Сравнение разных типов драйверов по ключевым параметрам

| Драйвер                                 |      | CML | LVDS | Pseudo<br>LVDS | SLVS | HSTL | VML<br>(SSTL) |

|-----------------------------------------|------|-----|------|----------------|------|------|---------------|

| Стандарт                                |      | 1   | +    | 1              | +    | +    | +             |

| Скорость передачи                       |      | ++  | _    | +              | +    | +    | +             |

| Потребляемая мощность                   |      |     | ++   | +              | ++   | +    | +             |

| Качество со-<br>гласования на<br>выходе |      | ++  | -    | ++             | -    | +    | +             |

| VDD,<br>B                               | 2,5  | ı   | +    | +              | +    | +    | +             |

|                                         | 1,8  | +   | I    | +              | +    | +    | +             |

|                                         | ≤1,2 | ±   |      |                | +    |      | +             |

| Рейтинг в Ин-<br>тернете                |      | 3   | 2    |                | 4    | 1    |               |

Помимо устройства СФ-блока самого МСПП, характеристики МСПП определяются системой параметров, зависящих от типа корпуса микросхемы и характеристик среды передачи, включая разъемы, сигнальные линии на печатной плате и соединительный кабель требуемой длины. Характеристики МСПП зависят также от внешних условий: помех и наводок от близкорасположенных приборов, рабочей температуры и т.д.

Современные разработки высокоскоростных МСПП.

Анализ современных работ показал, что большинство высокоскоростных приемопередатчиков работает на фиксированной скорости или на нескольких высоких скоростях в относительно узком диапазоне. Однако в реальных цифровых системах связи сохраняется потребность в высокоскоростных перестраиваемых МСПП с широким диапазоном битовых скоростей. В частности, такие перестраиваемые МСПП востребованы в отечественных разработках. Мультискоростные приемопередатчики

существенно сложнее в разработке за счет необходимости проектирования блоков программирования и коммутации скоростных режимов и сложности обеспечения в таком случае высоких технических характеристик проектируемых приемопередатчиков на всех скоростях.

#### ГЛАВА 2. Оценка показателя BER на этапе проектирования

Контроль уровня BER на этапе проектирования позволяет проводить оптимизацию блоков в составе МСПП с целью улучшения качества его работы. Анализ литературы показывает, что контроль показателя BER в процессе проектирования до сих пор полноценно не реализован, что ведет к итеративности расчетов, увеличивает их длительность и удорожает изготовленное изделие.

Оценка качества работы МСПП возможна как при измерении готовых образцов, так и при помощи моделей на этапе разработки. Известные автору методики оценки величины BER на этапе проектирования можно отнести к нескольким группам, приведенным на рисунке 3.

Рис. 3. Классификация методик оценки BER на этапе проектирования

Каждая из методик расчета величины ВЕR на этапе проектирования эффективна для определенного класса приемопередатчиков, а также на различных этапах разработки. Например, полностью аналитический метод и метод Монте-Карло полезен при анализе абстрактной архитектуры МСПП на верхнем уровне, когда модель тракта может быть идеализирована или достаточно проста для ускоренной оценочной симуляции. За основу разработанной методики был взят статистический подход (полуаналитический метод), поскольку он отличается высокой скоростью расчета и возможностью адаптации под множество архитектур приемопередатчиков, чья математическая модель может быть расширена и усложнена. В этом случае повышение точности результата достигается путем усложнения алгоритма обработки данных, а не увеличения их объема, как при моделировании или измерениях готовых образцов.

Поведенческое моделирование и характеризация при проектировании высокоскоростных приемопередатчиков.

Предложен комбинированный подход анализа целостности передаваемых данных на основе табличных моделей. Сначала в среде САПР определяются параметры поведенческих (табличных) моделей анализируемой части приемопередающего тракта на ограниченном интервале времени,

достаточного для затухания переходных процессов на выходе этой части после смены входного сигнала. Затем эти модели используются для продолжения расчетов с использованием специализированной математической программы, которая с той же точностью, что и САПР, но за гораздо меньшее время анализирует взаимодействие соседних передаваемых бит, возникающее вследствие межсимвольных интерференций. Предлагается дополнительно рассматривать стыки между цифровыми ядрами и периферийными частями в передатчике и приемнике.

Разработанная методика оценки уровня BER на этапе проектирования.

Предложена методика оценки BER на этапе проектирования.

Распределение плотности вероятностей возникновения битовой ошибки *DPC* имеет вид:

$$DPC = \frac{1}{\sigma^{\frac{2}{\sqrt{2\pi}}}} e^{\frac{(x-m)^2}{2\sigma^2}}, (1)$$

где  $\sigma$  — СКО распределения момента перепада уровня тактового сигнала внутри битового интервала, х — текущее значение момента перепада тактового сигнала, m — математическое ожидание момента перепада.

Для расчета BER полученное распределение интегрируется на интервалах, соответствующих появлению битовой ошибки (2):

$$BER = 1 - \int_0^{UI} DPC(t)dt$$

, (2)

где *UI* — битовый интервал сигнала данных.

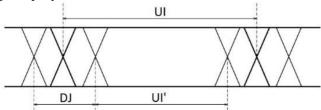

При этом предлагается учитывать уменьшение продолжительности битового интервала вследствие влияния джиттера тракта и минимальные времена предустановки и удержания триггеров приемника Tsetup<sub>min</sub> и  $Thold_{min}$ , см. рисунок 4.

Рис. 4. Уменьшение битового интервала

Таким образом, при интегрировании плотности распределения вероятностей формула (2) преобразуется в формулу (3):  $BER = 1 - \int_{(DJ/2) + Tsetup_{min}}^{UI - (DJ/2) - Thold_{min}} DPC(t) dt, (3)$

$$BER = 1 - \int_{(DJ/2) + Tsetup_{min}}^{UI - (DJ/2) - Thold_{min}} DPC(t)dt, (3)$$

Составляющими детерминированного джиттера *DJ* являются:

- Функциональный джиттер ФАПЧ передатчика  $DJ_{\Phi A\Pi Y}$ ;

- Джиттер цифровой части передатчика  $DJ_{TX\ DIG}$  и приемника  $DJ_{RX\ DIG}$ ;

- Джиттер драйвера передатчика  $DJ_{TX\ DR}$ ;

- Кодозависимый джиттер данных как следствие межсимвольной интерференции DJ<sub>INT</sub>;

- Джиттер усилителя приемника  $DJ_{RX\_AMP}$ ;

- Функциональный кодозависимый джиттер системы восстановления таковых сигналов из данных (ВТСД)  $DJ_{BTCД}$ ;

- Помехи по шине питания передатчика  $DJ_{TX\ VDD}$  и приемника  $DJ_{RX\ VDD}$ ;

- Неравномерность паразитных структур на шинах тактовых сигналов  $DJ_{CLK\ LAY}$ .

Одновременное влияния нескольких компонент джиттера может быть учтено суммированием:

$$DJ^{RX} = KBД(DJ_{\Phi A\Pi ' Y}) + KBД(DJ_{TX\_DIG}) + KBД(DJ_{TX\_DR}) + KBД(DJ_{INT}) + KBД(DJ_{RX\_AMP}) + KBД(DJ_{RX\_DIG}) + KBД(DJ_{TX\_VDD}) + KBД(DJ_{BTCД}) + KBД(DJ_{RX\_VDD}) + KBД(DJ_{CLK\_LAY}), (4)$$

где KBД — функция влияния джиттера входного сигнала на функциональный джиттер ВТСД приемника.

Приведенный ко входу триггеров приемника битовый интервал:

$$UI' = UI - DJ^{RX} - Tsetup_{min} - Thold_{min}$$

(5)

Разработанная модель учитывает различие в длинах битовых интервалов, зависящих от последовательности передаваемых данных. Алгоритм анализирует передаваемый код, составляя битовые шаблоны, которые учитывают предысторию длиной в несколько бит данных. Алгоритм рассчитывает вероятность появления того или иного шаблона, придавая им весовой коэффициент  $P_i$ :

$$P_i = \frac{D}{N} * M_i (6)$$

где D — длина шаблона в битах, N — общее число переданных бит,  $M_i$ — число повторов i-го шаблона в выборке из переданных бит.

Таким образом, окончательно BER будет являться алгебраической суммой BER для каждого из шаблонов с учетом их весовых коэффициентов:

$$BER = \sum_{i=1}^{n} (P_i * BER_i), (7)$$

где  $n=2^D$  — количество исследованных максимумов распределения. Ошибка приема может произойти при изменении логического уровня сигнала данных на одной из границ бита. Целесообразно рассматривать, помимо BER, частоту ошибок при передаче логических перепадов сигнала данных. Стандарт кодировки 8b/10b запрещает передачу шести и более нулей или единиц подряд. Усредненная частота перепадов логического уровня потока данных для кода 8b/10b имеет вид:

$$f_t = (N_1 + N_2 + N_3 + N_4 + N_5) * \frac{f_b}{M}, (8)$$

где  $f_t$  — частота перепадов логического уровня сигнала данных для кода 8b/10b,  $N_i$  — число последовательностей одинаковых бит длиной i, M — общее число бит в переданной посылке,  $f_b$  — битовая скорость передачи.

Данный подход позволяет получить более точное значение частоты битовых ошибок в процессе передачи произвольной посылки данных при известном алгоритме кодирования. Например, поток данных, закодированной по алгоритму 8b/10b, имеет усредненную частоту перепадов, в два раза меньшую, чем битовая скорость передачи. При оценке BER предлагается делать поправку на соотношение битовой частоты и усредненной частоты передаваемых перепадов логического уровня сигнала данных.

Используя данную методику, можно построить Bathtub Curve — параметрический график зависимости частоты ошибок от отношения сигнал/шум передаваемого потока данных. Параметром выступает положение восстановленного тактового сигнала в приемнике относительно принимаемого битового интервала.

Таким образом, предлагаемая методика оценки частоты возникновения битовых ошибок сводится к следующим шагам:

- Выбор кодовых последовательностей, для которых будет проводиться расчет;

- Анализ весовых коэффициентов (P<sub>i</sub>) шаблонов бит внутри последовательностей и расчет усредненной частоты изменения логического уровня потока данных;

- Расчет детерминированного джиттера цифрового тракта, линии передачи и функционального джиттера ВТСД для каждого шаблона бит;

- Расчет случайного джиттера ФАПЧ;

- Расчет случайного джиттера выходного тактового сигнала ВТСД относительно фазы потока данных;

- Приведение компонент джиттера ко входу триггеров первой ступени десериализации приемника;

- Интегрирование распределения плотности вероятностей с поправкой на частоту изменения логического уровня потока данных;

- Получение результирующего BER для каждой кодовой последовательности бит.

- Построение Bathtub Curve зависимости частоты ошибок от положения тактового сигнала триггера приемника относительно принимаемого битового интервала.

Использование разработанной методики на этапе проектирования позволяет выявить критичные блоки и провести их оптимизацию.

# ГЛАВА 3. Способы совершенствования критичных блоков и методика проектирования мультискоростных приемопередатчиков

Каждый блок в составе внутренней части МСПП, участвующий в формировании или тактировании передаваемых данных, вносит вклад в джиттер передаваемого сигнала.

Можно выделить следующие основные источники джиттера внутренней части МСПП:

- Блок фазовой автоподстройки частоты;

- Блок восстановления тактовых сигналов из данных;

- Стабилизатор питающего напряжения;

- Блок конвейера данных передатчика;

- Блок конвейера данных приемника.

Анализ вариантов реализации выходного мультиплексора передатчика.

Выходной мультиплексор передатчика является одним из наиболее важных блоков, так как он является последней ступенью свертки передаваемого потока данных. Такая свертка является битовой операцией. Рассинхронизация фаз сворачиваемых сигналов приводит к уменьшению эквивалентного битового интервала.

Приведен сравнительный анализ различных реализаций выходного мультиплексора передатчика. Мультиплексор 4 в 1, построенный на р-канальных ключах, является оптимальным и универсальным решением для широкого диапазона битовых скоростей. На рисунке 5 представлена топология такого мультиплексора.

Рис. 5. Топология мультиплексора 4 в 1 на р-канальных транзисторах Поиск оптимальной архитектуры цифровой части передатчика и приемника.

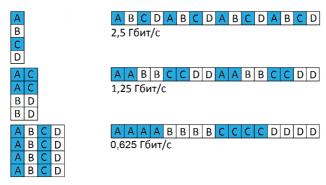

Цифровую часть передатчика и приемника можно разделить на область групповых операций (обработка несериализованных или частично сериализованных данных) и область битовых операций (обработка сериализованных данных). Программирование скорости передачи в широких пределах в области битовых операций ведет к повышению требований к быстродействию блоков вследствие необходимости построения сложных схем синхронизации цепей данных и тактовых сигналов. Программирование битовой частоты в области групповых операций позволяет снизить требования по быстродействию за счет некритичного увеличения занимаемой площади. Разработанные блоки битовых операций сериализации потока передаваемых данных запрограммированы на верхнюю битовую скорость Fbit (рисунок 6).

Параллельный код

Последовательный код

Рис. 6. Принцип форматирования данных на верхнюю частоту

Например, 2-битовый отрезок ab частоты Fbit= 1,25  $\Gamma\Gamma$ ц представлен кодовой группой aabb частоты Fbit= 2,5  $\Gamma\Gamma$ ц (2,5/1,25 = 2), что соответствует одному и тому же сигналу во временных координатах. В результате форматирования данных все частоты программируемой сетки не различимы в работе скоростных участков конвейера бит. Данный подход позволяет упростить архитектуру блоков, ускорить процесс синтеза схемы конвейера данных и сериализатора, а также снижает ограничения на цифровую часть МСПП по максимальной скорости передачи.

Произведен сравнительный анализ выходных мультиплексоров передатчика различной разрядности. Предложено применение фазового сдвига промежуточного потока данных для снижения требований по быстродействию для блоков цифровой части передатчика. Разработан набор технологически независимых синтезируемых Verilog блоков цифровой части передатчика и приемника.

Параметрическая стабилизация подблоков ФАПЧ и ВТСД.

Предложена схемотехническая реализация блоков, предназначенных для стабилизации полосы пропускания ФАПЧ и ВТСД при изменении параметров технологического процесса. В процессе разработки ФАПЧ необходимо достижение оптимальных значений таких характеристик ГУН, как диапазон перестройки частоты, спектральная плотность мощности шума и крутизна вольт-частотной характеристики (далее ВЧХ).

Принцип параметрической токовой стабилизации крутизны ГУН состоит в компенсации изменения режимного тока инвертирующей ячейки при параллельном подключении дополнительного источника тока  $I_{add}$ . Величина  $I_{add}$  зависит от параметров процесса и рабочей температуры. Приращения токов  $I_{cell}$  и  $I_{add}$  равны по модулю и имеют противоположные знаки, причем

$$I_{add} \sim \varphi_T \sim T$$

, (9)

где  $\varphi_T$  – температурный потенциал, T – абсолютная температура.

Результаты сравнения показывают, что относительно среднего значения разброс крутизны ВЧХ в случае без стабилизации составил 30%. В случае со стабилизацией разброс крутизны снизился и стал равен 14%. По сравнению со схемой без компенсации разброса режимного тока разброс крутизны ГУН уменьшен в 2.1 раза.

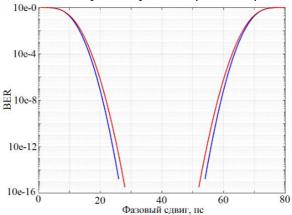

Аналогичным образом проделана параметрическая стабилизация тока зарядно-разрядного блока ФАПЧ (ЗРБ). Разброс тока ЗРБ в случае без стабилизации составил 15%. В случае со стабилизацией разброс крутизны снизился до 7%. На рисунке 7 представлена Bathtub curve для случаев со стабилизацией (синий график) и без стабилизации (красный график). Каждая пара кривых соответствует наихудшим нормам техпроцесса.

Рис. 7. Bathtub Curve тракта передачи для случаев со стабилизацией контура ФАПЧ (синий график) и без стабилизации (красный график) Оптимизация стабилизатора питающего напряжения.

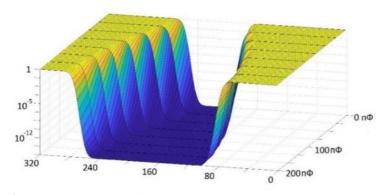

Предложен подход к оптимизации выходного напряжения стабилизатора с помощью разработанной методики оценки BER на этапе проектирования. С целью уменьшения взаимного влияния блоков друг на друга общие шины питания приемника и передатчика были разделены на области цифровых и аналоговых доменов. Каждый домен питается от понижающих стабилизаторов напряжения с 2,5 до 1,2 В. Это позволило снизить пульсации шины питания в три раза. На рисунке 8 изображена трехмерный Bathtub Curve, описывающая параметрическую зависимость частоты ошибок от демпфирующей емкости стабилизаторов напряжения передатчика.

Рис. 8. Трехмерный Bathtub Curve зависимости BER от номинала демпфирующего конденсатора стабилизаторов питания Методика проектирования МСПП, основанная на минимизации BER.

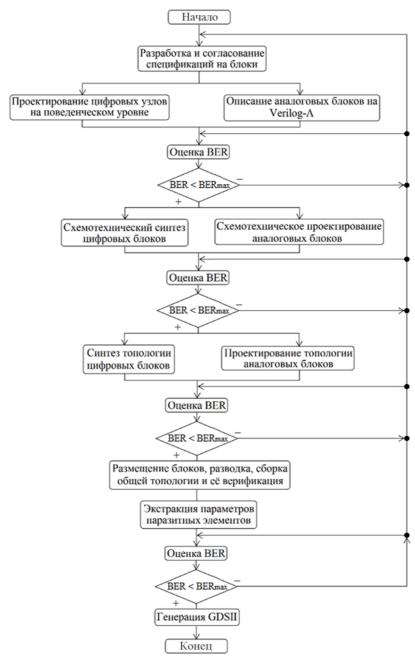

Суть алгоритма (рисунок 9) заключается в итерационном исследовании зависимости показателя BER от джиттера (случайного и детерминированного) критичных блоков с последующей их оптимизацией на всех этапах разработки. Методика оценки BER в данном случае служит инструментом определения запаса по фазовой ошибке между десериализуемыми данными и связанными с ними тактовыми сигналами приемника. В диссертации приводится пример расчета BER по данной методике.

Рис. 9. Методика проектирования МСПП с минимальным BER

#### ГЛАВА 4. Разработанные периферийные мультискоростные приемопередатчики, их расчетные характеристики и результаты экспериментальных испытаний

С использованием предложенных методики и маршрута был разработан и изготовлен ряд микросхем МСПП.

Приемопередатчик GigaSpaceWire по технологии КМОП HCMOS8D, 0,18 мкм.

Разработанный приемопередатчик работает в двух частотных диапазонах:

- 5–200 Мбит/с с шагом 5 Мбит/с;

- 312,5, 625, 1250 Мбит/с.

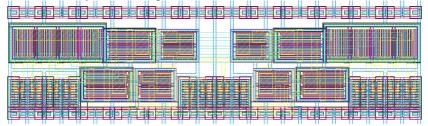

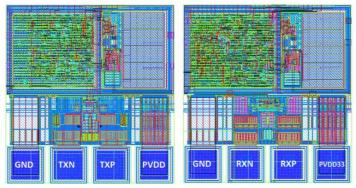

В процессе разработки проводился контроль оценочного уровня ВЕR в зависимости от характеристик и параметров критичных блоков. Автор принимал участие в разработке и верификации аналого-цифровых блоков сериализатора, десериализатора, блоков ФАПЧ и ВТСД. Измеренный ВЕR тестовых образцов по крайней мере меньше  $10^{-13}$ . На рисунке 10 представлена топология передатчика (слева) и приемника (справа). Ширина и высота каждого блока без контактных площадок составляют 470 мкм и 390 мкм соответственно.

Рис. 10. Разработанный передатчик и приемник GigaSpaceWire по КМОП технологии с нормами 180 нм

Приемопередатчик SpaceFibre по КМОП технологии TSMC с нормами 90 нм.

Разработанный приемопередатчик работает в двух частотных диапазонах:

- 5–200 Мбит/с с шагом 5 Мбит/с;

- 1250, 1562,5, 2500, 3125 Мбит/с.

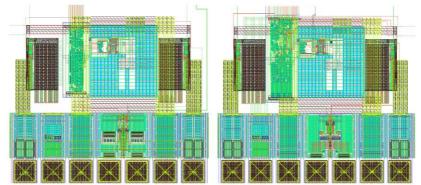

В процессе разработки также проводился контроль оценочного уровня BER. Данный МСПП содержит оптимизированные стабилизаторы питания, снижающие взаимовлияние блоков по шине питания. Измеренный BER тестовых образцов по крайней мере меньше  $10^{-13}$ . Автор

принимал участие в разработке и верификации аналого-цифровых блоков сериализатора, десериализатора, блоков ФАПЧ и ВТСД. Также автором проделана работа по схемотехнической и топологической интеграции блоков и проектирование топологии верхнего уровня передатчика и приемника. На рисунке 11 представлена топология передатчика (слева) и приемника (справа). Ширина и высота каждого блока без контактных площадок составляют 640 мкм и 493 мкм соответственно.

Рис. 11. Разработанный приемник SpaceFibre по КМОП технологии с нормами 90 нм

В таблице 2 приведено сравнение разработанного МСПП SpaceFibre по КМОП технологии TSMC с нормами 90 нм зарубежными аналогами.

Таблица 2. Сравнение разработанного МСПП по КМОП технологии TSMC с нормами 90 нм с зарубежными аналогами

| Обозначение   | Собствен-  | MAX9259/            | DS25BR204 | DS1021              |

|---------------|------------|---------------------|-----------|---------------------|

| Обозначение   |            |                     | D323DK204 | DS1021              |

|               | ная разра- | MAX9260             |           |                     |

|               | ботка      |                     |           |                     |

| Диапазон би-  | 5-3125     | 500–3125            | 400-3125  | 230–3200            |

| товых частот, |            |                     |           |                     |

| Мбит/с        |            |                     |           |                     |

| Технология    | КМОП 90    | КМОП 180            | _         | КМОП 65             |

| изготовления  | HM         | HM                  |           | HM                  |

| Напряжение    | 1,2/2,5    | 1,8/3,3             | 3,3       | 1,2/3,3             |

| питания, В    |            |                     |           | , ,                 |

| Джиттер на    | 0,125      | 0,25                | 0,15      | 0,35                |

| частоте 3,125 |            |                     | ·         |                     |

| Гбит/с, UI    |            |                     |           |                     |

| BER           | < 10-13    | < 10 <sup>-12</sup> | _         | < 10 <sup>-12</sup> |

| Интерфейс     | CML        | CML                 | CML/      | CML                 |

| обмена        |            |                     | LVDS/     |                     |

|               |            |                     | LCPECL    |                     |

| Рабочая тем- | -60–125  | -40–120 | -40–85  | -40–100 |

|--------------|----------|---------|---------|---------|

| пература     |          |         |         |         |

| Тип корпуса  | LQFP-176 | TQFP-64 | WQFN-40 | WLCS    |

Приемопередатчик SpaceFibre по КМОП технологии TSMC с нормами 40 нм.

Разработанный приемопередатчик работает в частотном диапазоне:

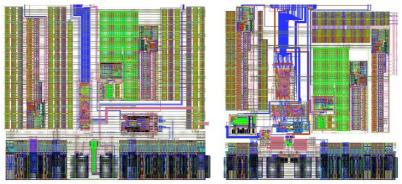

• 1250, 2500(3125), 5000(6250), 10000(12500) Мбит/с.

В процессе разработки также проводился контроль оценочного уровня ВЕR. Автор принимал участие в разработке и верификации аналогоцифровых блоков сериализатора, десериализатора. Также автором проделана работа по схемотехнической и топологической интеграции блоков и проектирование топологии верхнего уровня передатчика и приемника. На рисунке 12 представлена топология передатчика (слева) и приемника (справа). Ширина и высота передатчика составляют 630 мкм и 531 мкм, приемника – 563 и 531 мкм соответственно.

Рис. 12. Разработанный приемник SpaceFibre по КМОП технологии с нормами 40 нм

#### Заключение

Основной результат диссертации заключается в решении актуальной задачи развития теории и создании методики проектирования мультискоростных гигабитных приемопередатчиков последовательного канала, а также разработке на этой основе конкурентоспособных сложно-функциональных блоков приемопередатчиков, рассчитанных на диапазон битовых скоростей от 5 Мбит/с до 12,5 Гбит/с, изготовленных по объемной КМОП технологии с проектными нормами от 180 до 40 нм и удовлетворяющих требованиям современной электронной компонентной базы.

#### Основной теоретический результат

В диссертации разработана методика проектирования МСПП, призванная контролировать показатель качества работы ВЕК на всех этапах разработки. Методика основана на предложенной полуаналитической модели МСПП, учитывающей вклад в вероятность появления битовой

ошибки в критичных блоках в составе МСПП. Данная методика позволяет на порядки сократить время оценки BER критичных блоков МСПП на этапе проектирования. Её использование в сочетании с известными способами и средствами построения периферийных блоков позволяет реализовать полный маршрут проектирования гигабитных МСПП.

## Частные теоретические результаты

- 1. Разработана новая полуаналитическая модель тракта передачи, которая предусматривает анализ передаваемых кодовых последовательностей на основе выборок с присвоением весовых коэффициентов.

- 2. Впервые помимо показателя BER обосновано использование частоты ошибок при передаче логического перепада как интегрального показателя качества работы приемопередатчиков последовательного канала, не зависящего от кодовой последовательности.

- 3. Предложен метод стабилизации полосы пропускания ФАПЧ в диапазоне температур и с учетом разбросов технологического процесса, основанный на параметрической стабилизации блоков в составе контура ФАПЧ.

# Основной практический результат

На основе предложенной методики разработаны и изготовлены по технологии с проектными нормами от 180 до 40 нм СФ блоки гигабитных МСПП со скоростью передачи от 5 Мбит/с до 12,5 Гбит/с. Получены работоспособные образцы.

# Частные практические результаты

- 1. Методика расчета показателя BER на этапе проектирования использована при разработке критичных заказных блоков высокоскоростных приемопередатчиков последовательного канала, работающих на скоростях от 5 Мбит/с до 12,5 Гбит/с по КМОП технологиям объемного кремния уровня от 180 нм до 40 нм.

- 2. Методика проектирования приемопередатчиков последовательного канала, основанная на анализе и минимизации показателя BER, использована при разработке оптимальной архитектуры конвейера данных передатчика и приемника, а также при обосновании эффективности метода форматирования битовой скорости передачи.

- 3. Выполнено объективное сравнение различных вариантов реализации устройств физического уровня на основе эскизного проектирования этих устройств с интерфейсами LVDS, VML, HSTL и CML по КМОПтехнологии и даны рекомендации по их использованию.

- 4. Предложен подход к высокоуровневому моделированию приемопередающих трактов с использованием поведенческих (табличных) моделей выбранных частей этих трактов, сочетающий преимущество результатов расчетов с помощью САПР сквозного проектирования по точности со сниженным временем расчетов при высокоуровневом моделировании. Написана и отлажена в среде пакета SciLab

- специализированная программа анализа приемопередающих трактов с использованием поведенческих (табличных) моделей.

- 5. Разработаны и реализованы блоки ФАПЧ с улучшенными точностными характеристиками: зарядно-разрядный блок с компенсацией дрейфа крутизны вольт-частотной характеристики генератора, управляемого напряжением (ГУН), ГУН со стабилизированной крутизной вольт-частотной характеристики, фильтр ФАПЧ с настраиваемыми параметрами в зависимости от битовой скорости данных. Использование этих блоков в составе спроектированных высокоскоростных приемопередатчиков позволило обеспечить требуемую совокупность параметров элементов ФАПЧ в диапазоне рабочих температур, технологического разброса элементов схем, а также битовых скоростей.

- 6. Разработаны и использованы при проектировании МСПП набор технологически независимых синтезируемых Verilog блоков цифровой части передатчика и приемника, а также архитектура конвейера данных, включающая в себя принципы программирования битовой скорости, фазового сдвига потока данных и выбора оптимальной разрядности шины тактовых сигналов битовых операций.

Таким образом, в ходе работы над диссертацией достигнута её основная цель, а именно повышение надежности передачи информации по последовательным каналам периферийными мультискоростными приемопередатчиками за счет снижения относительного числа битовых ошибок путем применения при проектировании приемопередатчиков предложенной полуаналитической модели тракта передачи. Разработаны отечественные МСПП по проектным нормам от 180 до 40 нм работающие в диапазоне скоростей передачи от 5 Мбит/с до 12,5 Гбит/с с частотой битовых ошибок не более  $10^{-12}$ .

# Список работ, опубликованных по теме диссертации

# 1. Публикации в журналах из перечня Scopus/ Web of Science:

- D.A. Domozhakov, S.V. Kondratenko. Specialized Methods and Tools for Accelerated Characterization of High-Speed Serial Transceivers // J. Commun. Technol. Electron. 2021. PP. 887–894.

- D.A. Domozhakov, Design Experience of a Multispeed Transmitter Manufactured by 90-nm CMOS Technology and Intended to Work in the Space-Fibre Serial Channel // J. Commun. Technol. Electron. 2021. PP. 989–996.

- 3. A. A. Garmash, D. A. Domozhakov and N. Y. Rannev. Bit error rate evaluation in high speed communication channels // 2nd International Telecommunication Conference Advanced Micro- And Nanoelectronic Systems And Technologies. 2019. PP. 012011.

- 4. A. V. Dubinskiy, D. A. Domozhakov and N. U. Rannev. Design of clock and data recovery system's behavioral model for high speed transceivers of serial interfaces // ITM Web of Conferences. 2019.

#### 2. Публикации в журналах из перечня ВАК РФ:

- 1. Доможаков Д.А., Кондратенко С.В. Поведенческое моделирование и характеризация при проектировании высокоскоростных приемопередатчиков // Вопросы радиоэлектроники. Сб. науч. тр. М.: ЦНИИ "Электроника". 2019. С. 64–70.

- 2. Доможаков Д.А., Кондратенко С.В. Специализированные методы и средства ускоренной характеризации высокоскоростных приемопередатчиков последовательных каналов // Радиотехника и электроника. Т. 66, № 7. 2021. С. 717-724.

- 3. Доможаков Д.А. Опыт проектирования мультискоростного приемопередатчика, изготовленного по КМОП технологии 90 нм и предназначенного для работы в последовательном канале SpaceFibre // Радиотехника и электроника. Т. 66, № 8. 2021. С. 825-832.

- 4. Доможаков Д. А. Генератор, управляемый напряжением, с токовой компенсацией влияния технологического процесса и рабочей температуры // Электронная техника. Серия 3: микроэлектроника. Сб. науч. тр., н. 1, М.: НИИМЭ. 2019. С. 27–31.

- 5. Алексеев И. Н., Байков В. Д., Глушков А. В., Доможаков Д. А., Дубинский А. В., Раннев Н. Ю. Проблемы повышения скоростных характеристик приемопередатчиков портов SpaceFibre // Международный форум «Микроэлектроника-2018». Сборник докладов, Спецвыпуск (89) Нано-индустрия. 2019. С. 219–230.

- 6. Байков В.Д., Доможаков Д.А., Дубинский А.В. Методика оценки вероятности возникновения битовых ошибок в приемопередатчиках SpaceFibre // Международный форум «Микроэлектроника-2018». Сборник докладов, Спецвыпуск (89) Наноиндустрия. 2019. С. 287–296.

- 7. Доможаков Д.А., Кондратенко С.В. Особенности обработки особых ситуаций в высокоскоростных приемниках последовательных каналов // Вопросы радиоэлектроники. Сб. науч. тр. М.: ЦНИИ "Электроника". 2018. С. 27–32.

- 8. Доможаков Д.А., Кондратенко С.В. Опыт и методика проектирования высокоскоростных приемопередатчиков последовательных каналов // Вопросы радиоэлектроники. Сб. науч. тр. М.: ЦНИИ "Электроника". 2018. С. 6–9.

- 9. Доможаков Д.А., Дубинский А.В., Раннев Н.Ю. Методика расчёта вероятности возникновения ошибок в высокоскоростных каналах связи // Проблемы разработки перспективных микро- и наноэлектронных систем (МЭС). Сб. науч. тр. 2016. С. 164–169.

- 10. Герасимов Ю.М., Доможаков Д.А., Кондратенко С.В., Ломакин С.С., Солохина Т.В. Варианты реализации высокоскоростных КМОП приемопередатчиков на физическом уровне // Проблемы разработки

- перспективных микро- и наноэлектронных систем (МЭС). Сб. науч. тр. 2014. С. 71–76.

- 11. Гармаш А.А., Дубинский А.В., Доможаков Д.А., Кобыляцкий А.В. Влияние паразитных конструктивных элементов на характеристики качества СФ-блоков синтезаторов частот в составе КМОП СБИС // Вопросы радиоэлектроники. Сб. науч. тр. М.: ЦНИИ "Электроника". 2013. С. 79—89.

#### 3. Зарегистрированные результаты интеллектуальной деятельности:

- 1. Динамический D-триггер: Пат. RU 182852 U1 Poc. Федерация/ Байков В. Д., Доможаков Д. А., Дубинский А. В., Кобыляцкий А. В., Петричкович Я. Я.; № 2018123467; заявл. 28.06.2018; опубл. 04.09.2018; АО НПЦ "ЭЛВИС".

- Динамический D-триггер: Пат. RU 182981 U1 Рос. Федерация/ Байков В. Д., Доможаков Д. А., Дубинский А. В., Кобыляцкий А. В., Петричкович Я. Я.; № 2018111875; заявл. 03.04.2018; опубл. 06.09.2018; АО НПЦ "ЭЛВИС".

- 3. Динамический D-триггер: Пат. RU 2679220 C1 Рос. Федерация/ Байков В. Д., Доможаков Д. А., Дубинский А. В., Кобыляцкий А. В., Петричкович Я. Я.; № 2018111868; заявл. 03.04.2018; опубл. 06.02.2019; АО НПЦ "ЭЛВИС".

#### 4. Участие в конференциях.

- 1. Всероссийская научно-техническая конференция "Проблемы разработки перспективных микро- и наноэлектронных систем": 2014 г. и 2016 (г. Зеленоград). Доклад «Методика расчёта вероятности возникновения ошибок в высокоскоростных каналах связи» (2016). Соавтор доклада «Варианты реализации высокоскоростных КМОП приемопередатчиков на физическом уровне» (2014).

- 2. Научная сессия МИФИ, 2015 г. Доклад «Методика расчета вероятности возникновения ошибок в высокопроизводительных каналах связи».

- 3. Международный Форум «Микроэлектроника 2018», г. Алушта. Два доклада. «Проблемы повышения скоростных характеристик приемопередатчиков портов SpaceFibre», «Методика оценки вероятности возникновения битовых ошибок в приемопередатчиках SpaceFibre».